資源簡介

該設計的頻率和脈沖占空比都可變,且由外部輸入引腳進行配置;其中可變周期(00表示40ms、01表示80ms、10表示120ms、11表示400ms),可變占空比(1/256~255/256);最終在Cyclone 系列FPGA進行驗證,滿足要求。

代碼片段和文件信息

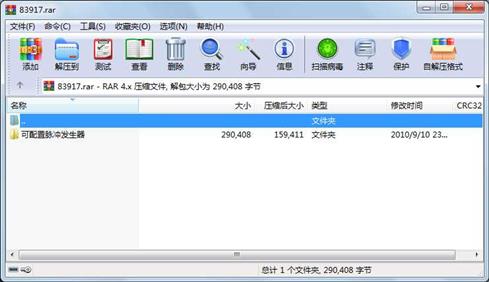

?屬性????????????大小?????日期????時間???名稱

-----------?---------??----------?-----??----

?????文件?????280576??2010-09-10?23:33??可配置脈沖發生器\FPGA課程設計報.doc

?????文件???????9832??2010-09-10?23:29??可配置脈沖發生器\pulse_generator.v

?????目錄??????????0??2010-09-10?23:34??可配置脈沖發生器

-----------?---------??----------?-----??----

???????????????290408????????????????????3

-----------?---------??----------?-----??----

?????文件?????280576??2010-09-10?23:33??可配置脈沖發生器\FPGA課程設計報.doc

?????文件???????9832??2010-09-10?23:29??可配置脈沖發生器\pulse_generator.v

?????目錄??????????0??2010-09-10?23:34??可配置脈沖發生器

-----------?---------??----------?-----??----

???????????????290408????????????????????3

評論

共有 條評論

川公網安備 51152502000135號

川公網安備 51152502000135號