資源簡介

基于MIPS指令集的32位五級流水線的CPU設(shè)計與Verilog實現(xiàn)。該CPU可以實現(xiàn)28條基本指令。基于SMIC 0.25μm工藝庫,使用Design Compile與NC Verilog對設(shè)計分別進行邏輯綜合和后仿,根據(jù)面積、時序等信息對設(shè)計進行了優(yōu)化。最后,為該CPU添加了共享總線,以及UART與GPIO接口,實現(xiàn)了一個簡單的SoC,并編寫了測試代碼,在Modelsim上完成了功能仿真和時序仿真。

代碼片段和文件信息

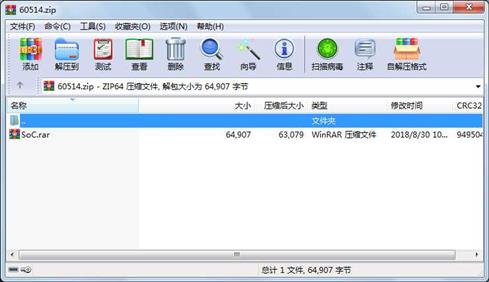

?屬性????????????大小?????日期????時間???名稱

-----------?---------??----------?-----??----

?????文件???????64907??2018-08-30?10:02??SoC.rar

-----------?---------??----------?-----??----

?????文件???????64907??2018-08-30?10:02??SoC.rar

評論

共有 條評論

川公網(wǎng)安備 51152502000135號

川公網(wǎng)安備 51152502000135號